- Joined

- Dec 11, 2018

- Messages

- 1,237

- Trophies

- 0

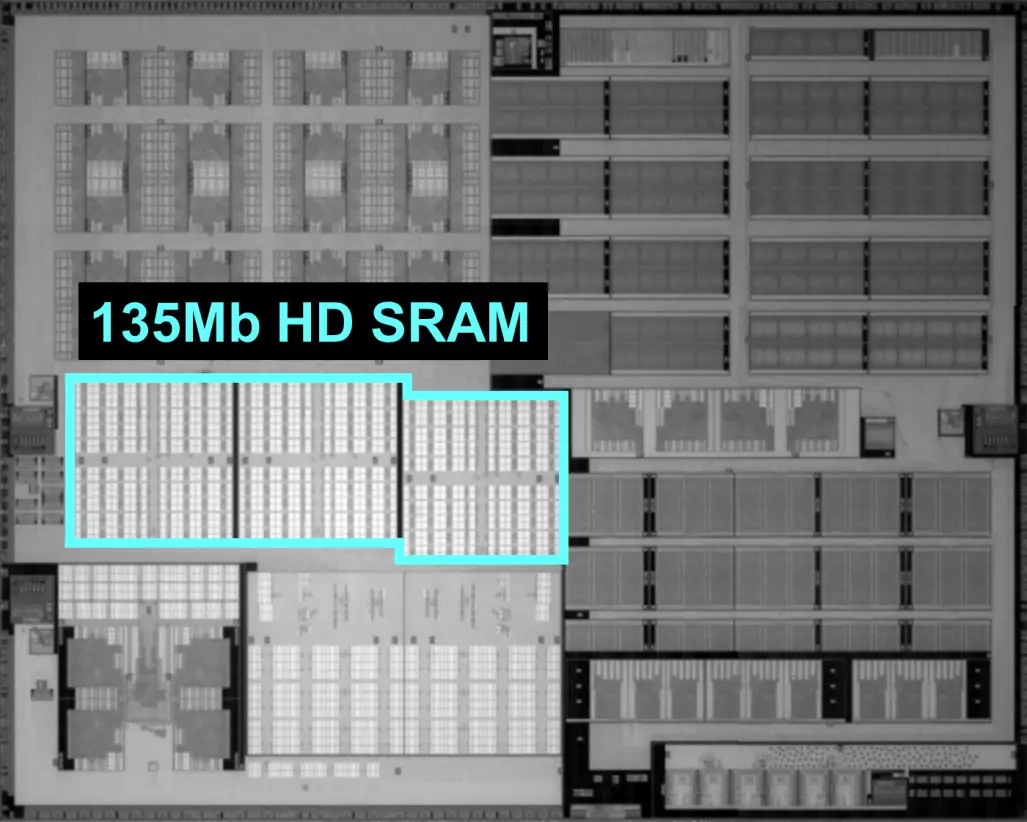

TSMC says it expects its N5 node to ramp even quicker. 5-nanometer entered risk production in March 2019. The process is expected to ramp in Q2 this year – likely in April or May. When ramped, this will be the densest process in terms of both transistor density and SRAM density – leapfrogging both Samsung and Intel. Samsung 5-nanometer is only slightly denser than their 7-nanometer and is not competitive with TSMC 5 nm. Samsung’s next big jump is their 3-nanometer node. Intel will likely capture the density lead with their 7-nanometer node, however, that node isn’t coming until late next year – a solid 1.5 years behind.

TSMC Details 5 nm

TSMC details its 5-nanometer node for mobile and HPC applications. The process features the industry's highest density transistors with a high-mobility channel and highest-density SRAM cells.

fuse.wikichip.org

fuse.wikichip.org

With regards to 5nm manufacturing, TSMC is already at the beginning stages and will ramp up early production later this year. These are basically prototype designs. Which brings us to the bit that's interesting.

"At IEDM, TSMC reported 1.84x density improvement over the company’s own N7 node. Our estimates land at 1.87x which is reasonably close. A ramp in April will mark exactly two years since TSMC ramped its 7-nanometer node," WikiChips says.

An 84-87 percent increase in transistor density compared to current 7nm designs is significant. Transistor density has traditionally been an indicator of overall performance, and while it's more complicated than that—this is where the rabbit hole runs deep, if you care to dig around the web—AMD could potentially see major gains in both compute performance and power efficiency with Zen 4.

AMD's 5nm CPUs could be monsters if TSMC's transistor numbers are right

If the transistor density predictions are accurate, Zen 4 will be a beast.